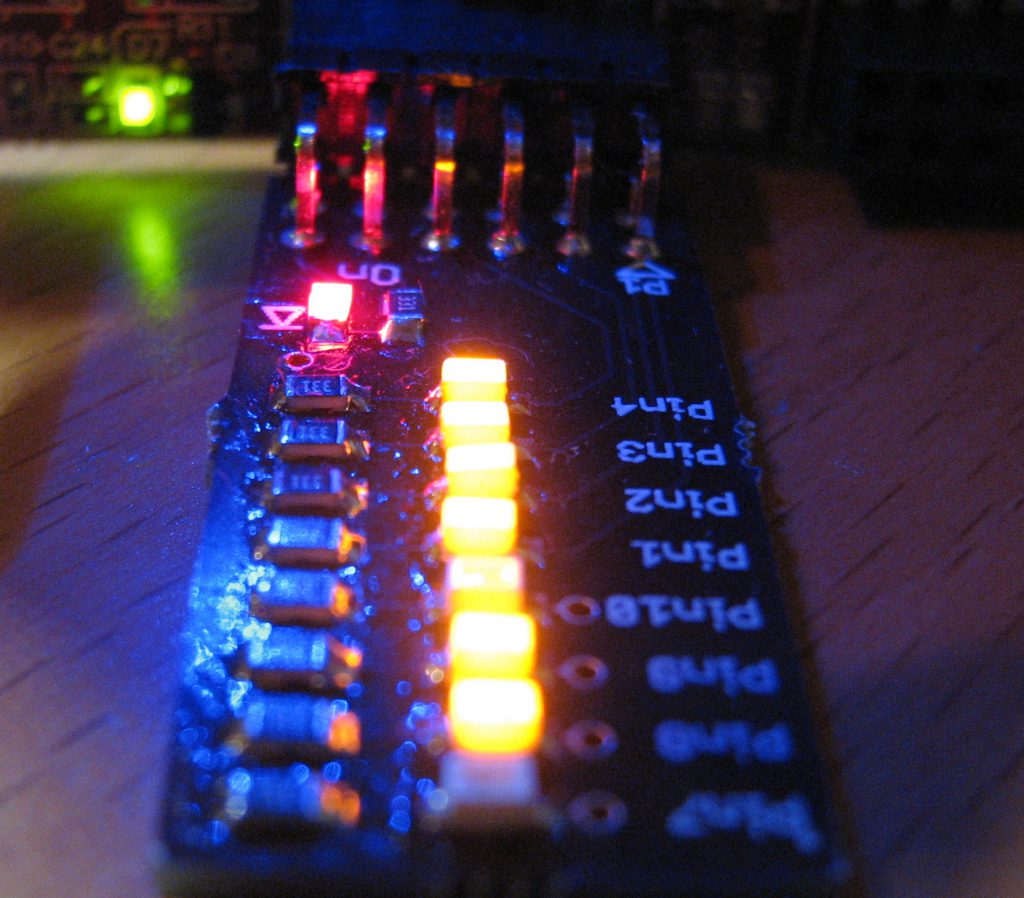

Not your traditional “Hello World”, but it fits the world we live in.

Verilog:

module TinyFPGA_A1 (

inout pin1,

inout pin2,

inout pin3_sn,

inout pin4_mosi,

inout pin5,

inout pin6,

inout pin7_done,

inout pin8_pgmn,

inout pin9_jtgnb,

inout pin10_sda,

inout pin11_scl,

inout pin16,

inout pin17,

inout pin18_cs,

inout pin19_sclk,

inout pin20_miso,

inout pin21,

inout pin22

);

assign pin1 = LED_dp;

assign pin2 = SEG_OUT[2]; // c

assign pin3_sn = SEG_OUT[1]; // b

assign pin4_mosi = SEG_OUT[0]; // a

assign pin19_sclk = SEG_OUT[5]; // f

assign pin20_miso = SEG_OUT[6]; // g

assign pin21 = SEG_OUT[4]; // e

assign pin22 = SEG_OUT[3]; // d

assign pin9_jtgnb = led_timer[20];

assign pin10_sda = led_timer[19];

assign pin11_scl = led_timer[18];

reg [6:0] SEG_OUT;

wire clk;

OSCH #(

.NOM_FREQ(“2.08”)

) internal_oscillator_inst (

.STDBY(1’b0),

.OSC(clk)

);

reg LED_dp;

reg [24:0] led_timer;

always @(posedge clk) begin

led_timer <= led_timer + 1;

//end

//always @(led_timer[22:18]) begin

case (led_timer[24:20])

4’h0: SEG_OUT = 7’b0111111;

4’h1: SEG_OUT = 7’b0000110;

4’h2: SEG_OUT = 7’b1011011;

4’h3: SEG_OUT = 7’b1001111;

4’h4: SEG_OUT = 7’b1100110;

4’h5: SEG_OUT = 7’b1101101;

4’h6: SEG_OUT = 7’b1111101;

4’h7: SEG_OUT = 7’b0000111;

4’h8: SEG_OUT = 7’b1111111;

4’h9: SEG_OUT = 7’b1100111;

4’hA: SEG_OUT = 7’b1110111;

4’hB: SEG_OUT = 7’b1111100;

4’hC: SEG_OUT = 7’b0111001;

4’hD: SEG_OUT = 7’b1011110;

4’hE: SEG_OUT = 7’b1111001;

4’hF: SEG_OUT = 7’b1110001;

default: SEG_OUT = 7’b1001001;

endcase

end

endmodule